This post introduces solutions to new challenges in E/E architecture.

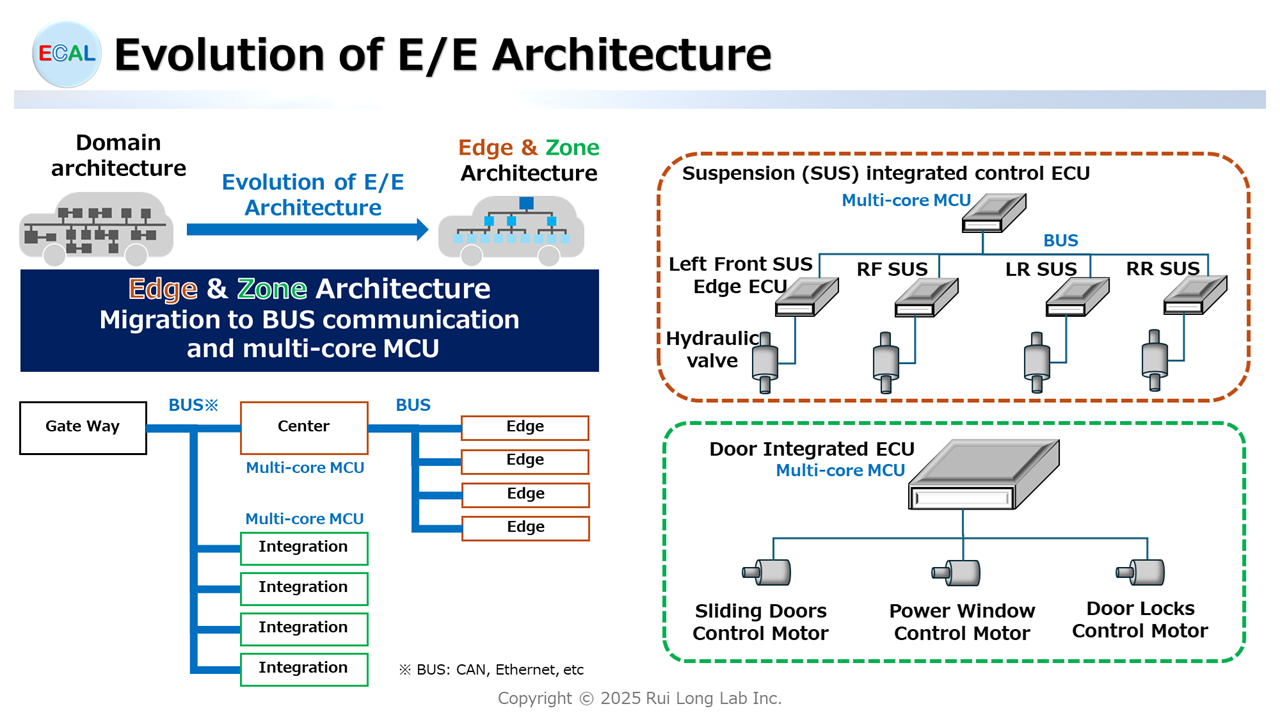

Evolution of E/E Architecture

The E/E architecture is transitioning from traditional domain-based architectures toward edge-based and zone-based architectures. In these new architectures, BUS communication and the core-shared BUS in multi-core microcontrollers will play a central role.

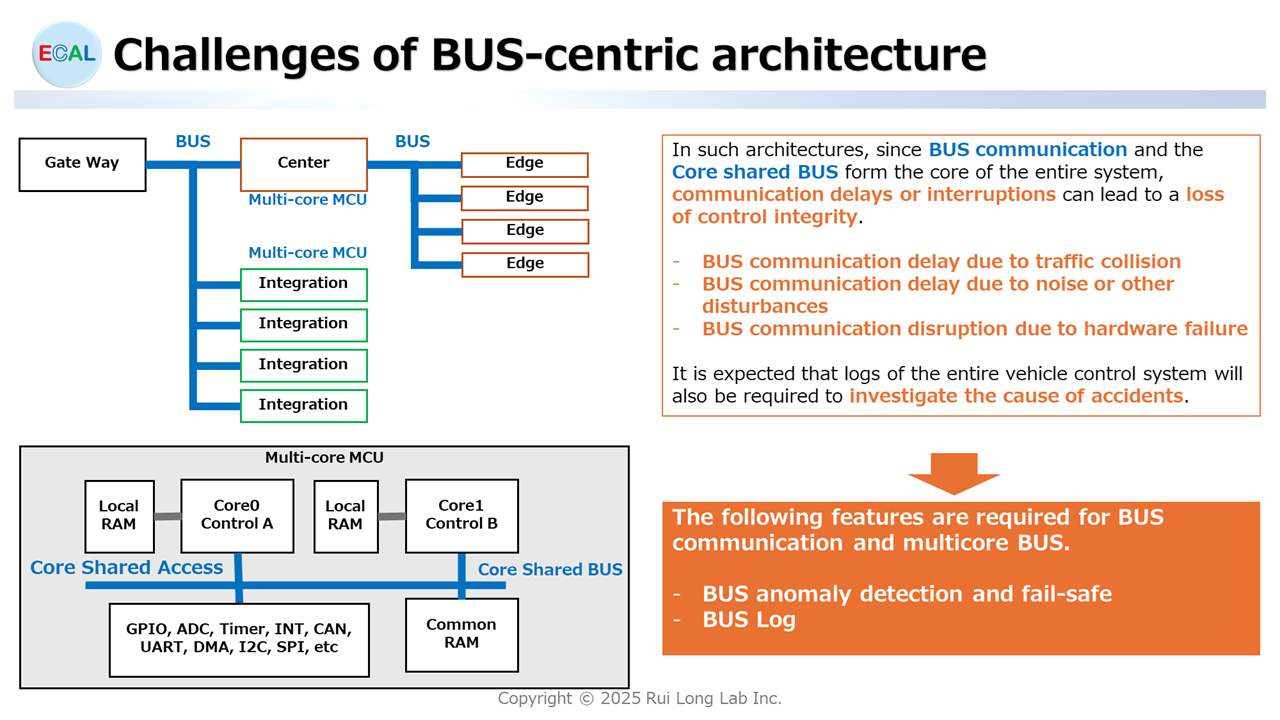

Challenges of BUS-centric architecture

In such an architecture, as shown in the figure below, the bus communication and core common bus form the backbone of the entire system. Consequently, communication delays or interruptions can lead to a loss of control integrity. Furthermore, it is anticipated that logs covering the entire vehicle control system will be required for accident cause investigations.

Therefore, the following functions are required for the BUS communication and the Core shared BUS.

- BUS anomaly detection and fail-safe

- BUS Log

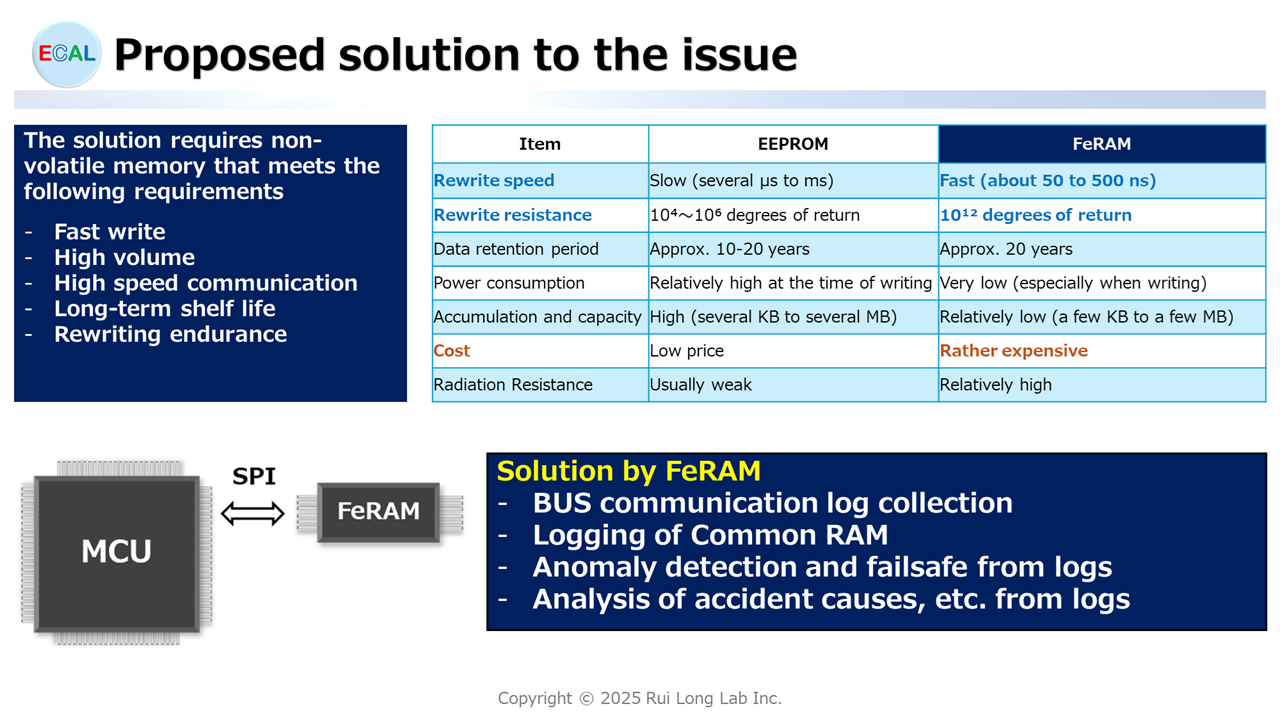

Proposed solution to the issue

To achieve the required functionality, we propose the solution illustrated below. Please note that this post is merely a proposal.

RAMXEED FeRAM MB85RS4MTY specification

| Item | performance | Notes |

|---|---|---|

| Memory capacity | 512 k × 8bit | |

| Communication speed | 50Mbps | SPI |

| Waiting time for posting | zero | |

| Write/read tolerance | 1014 times | |

| Data retention characteristics | 50.4 years (+85°C) 13.7 years (+105°C) 4.2 years (+125°C) | |

| Ambient operating temperature | -40°C ~ +125°C | |

| Operating supply voltage | 1.8V~3.6V | |

| Quality/Reliability | AEC-100 compliant | |

| Example: Number of CAN ID logs Log time | 78ID×8byte 6.06s | Calculation conditions: 500kbps, 111bit/ID, 30% CAN BUS utilization. |

| Example: Number of logs in Common RAM Logging time | 600 byte 0.865s | Calculation conditions: Control cycle 1ms |

If you are interested, please contact us here.