この投稿では、CPUについて説明します。

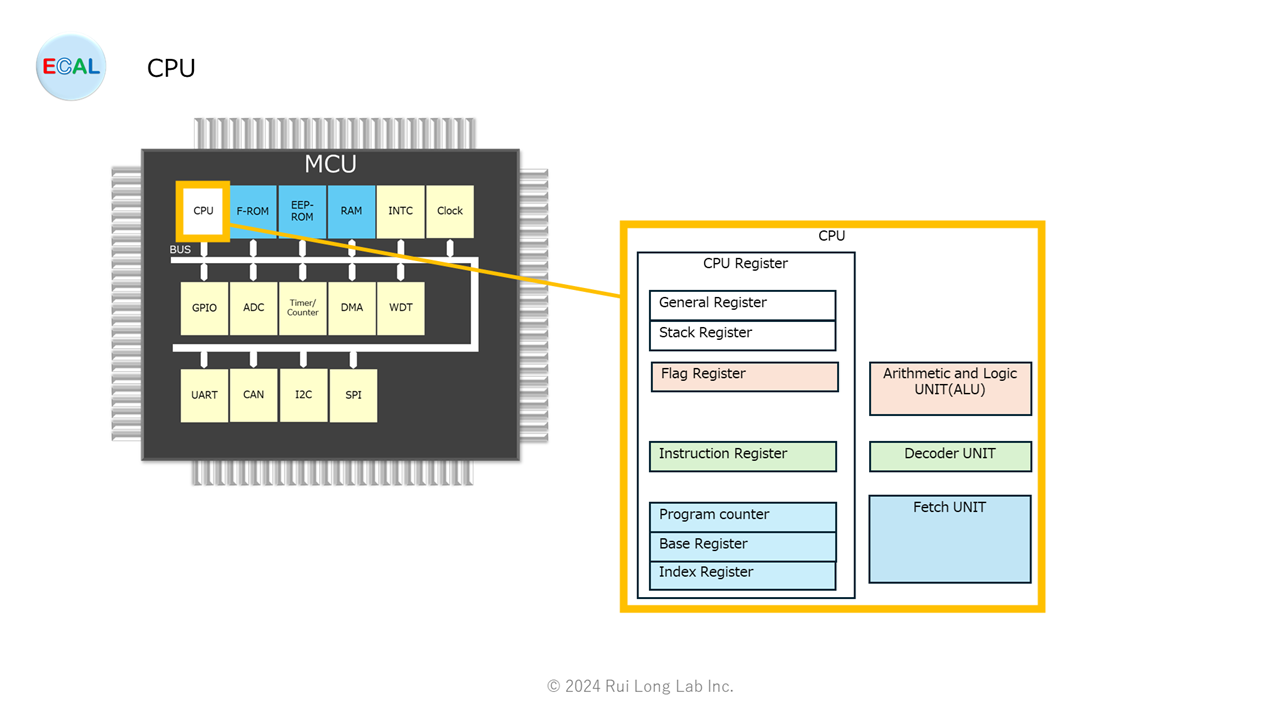

CPU

CPUは、CPUレジスタ (CPU Register)とALU (Arithmetic and Logic UNIT) 、デコーダユニット (Decoder UNIT)、フェッチユニット (Fetch UNIT)で構成されています。

CPUレジスタ(CPU Register)

CPUレジスタは、汎用レジスタ (General Register) やスタックレジスタ (Stack Register)、フラグレジスタ (Flag Register)、命令レジスタ (Instruction Register)、プログラムカウンタ (Program Counter)、ベースレジスタ (Base Register)、インデックスレジスタ (Index Register) などで構成されています。

汎用レジスタ(General Register)

汎用レジスタ は、汎用的に使用することが出来るレジスタです。

スタックレジスタ (Stack Register)

スタックレジスタは、スタックポインタの先頭アドレスを保存するレジスタです。

フラグレジスタ (Flag Register)

フラグレジスタは、ALUで行った演算の結果が、正の値なのか負の値なのか、オーバフローやアンダーフローが発生しているかなどを保存するレジスタです。

命令レジスタ (Instruction Register)

命令レジスタは、命令コードをフェッチした際に命令コードを保存するレジスタです。

プログラムカウンタ (Program Counter)

プログラムカウンタは、次に実行する命令コードが保存されているアドレス値を保存するレジスタです。

ベースレジスタ (Base Register)

ベースレジスタは、アクセスしたい記憶領域の先頭アドレスを保存するレジスタです。

インデックスレジスタ (Index Register)

インデックスレジスタは、ベースレジスタを基準にアクセスしたい記憶領域のアドレスとの相対アドレスを保存するレジスタです。

ALU

ALUは、加算器と論理演算器などの演算回路で構成されており、基本的な四則演算である加算、減算、乗算、除算および、OR(論理和)、AND(論理積)、NOR(排他的論理和)などの論理演算を行うユニットです。

デコーダユニット (Decoder UNIT)

デコーダユニットは、メモリから読み出した命令コードを解読し、CPUレジスタ、ALU、メモリを制御するユニットです。

フェッチユニット (Fetch UNIT)

フェッチユニットは、プログラムカウンタに保存されているアドレスから命令コードを呼び出して命令レジスタに保存(フェッチ)を行うユニットです。

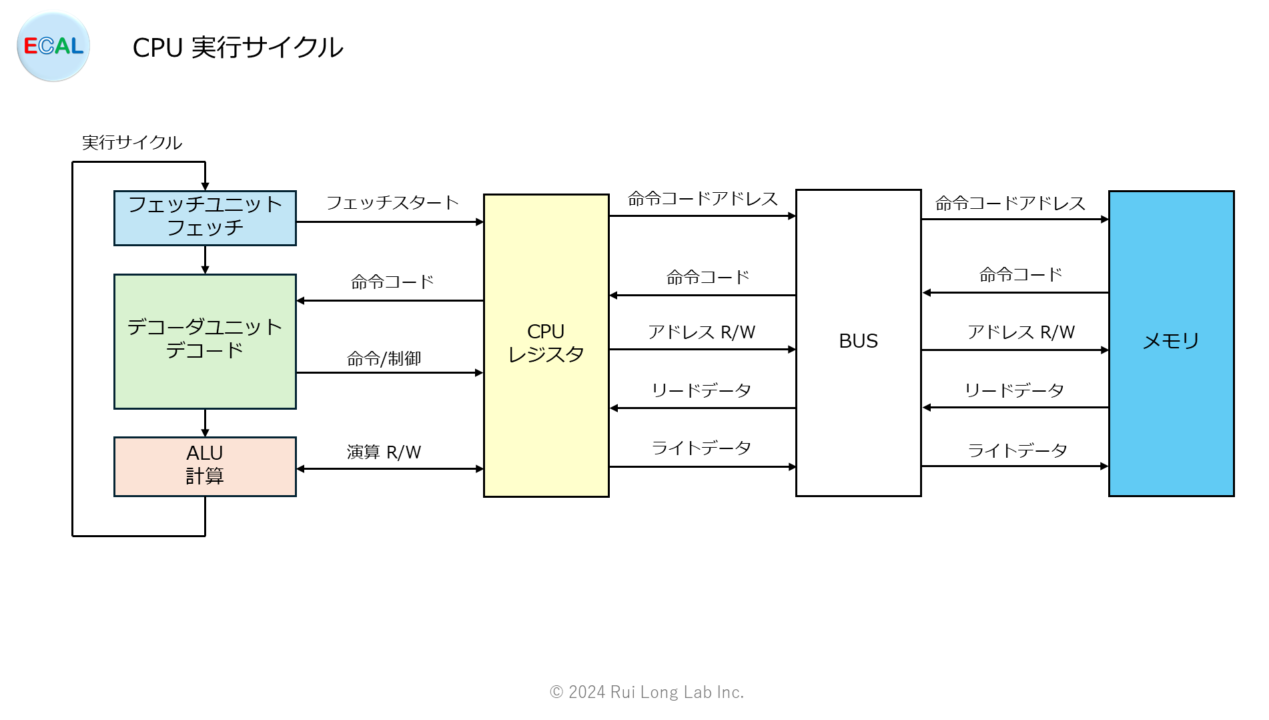

CPUの実行サイクル

CPUの実行サイクルは、フェッチ (Fetch)、デコード (Decode)、命令の実行 (Execut)を繰り返して実行します。

フェッチ (Fetch)

フェッチは、プログラムカウンタに保存されている命令コードのメモリアドレスから命令コードをReadし、Readした命令コードを命令レジスタに保存します。プログラムカウンタは、次の命令コードアドレスにインクリメントします。

デコード (Decode)

デコードは、命令レジスタに保存されている命令コードを解読し、命令コードの対象となるデータの実行アドレスを計算し、その実行アドレスからデータを汎用レジスタに保存する。

命令の実行 (Execut)

命令の実行は、命令コードを実行することです。例えば命令コードが計算の場合、デコードで保存した汎用レジスタの値をALUで演算し、その結果を汎用レジスタに保存する。