この投稿では、E/Eアーキテクチャの新たな課題の解決案を紹介させていただきます。

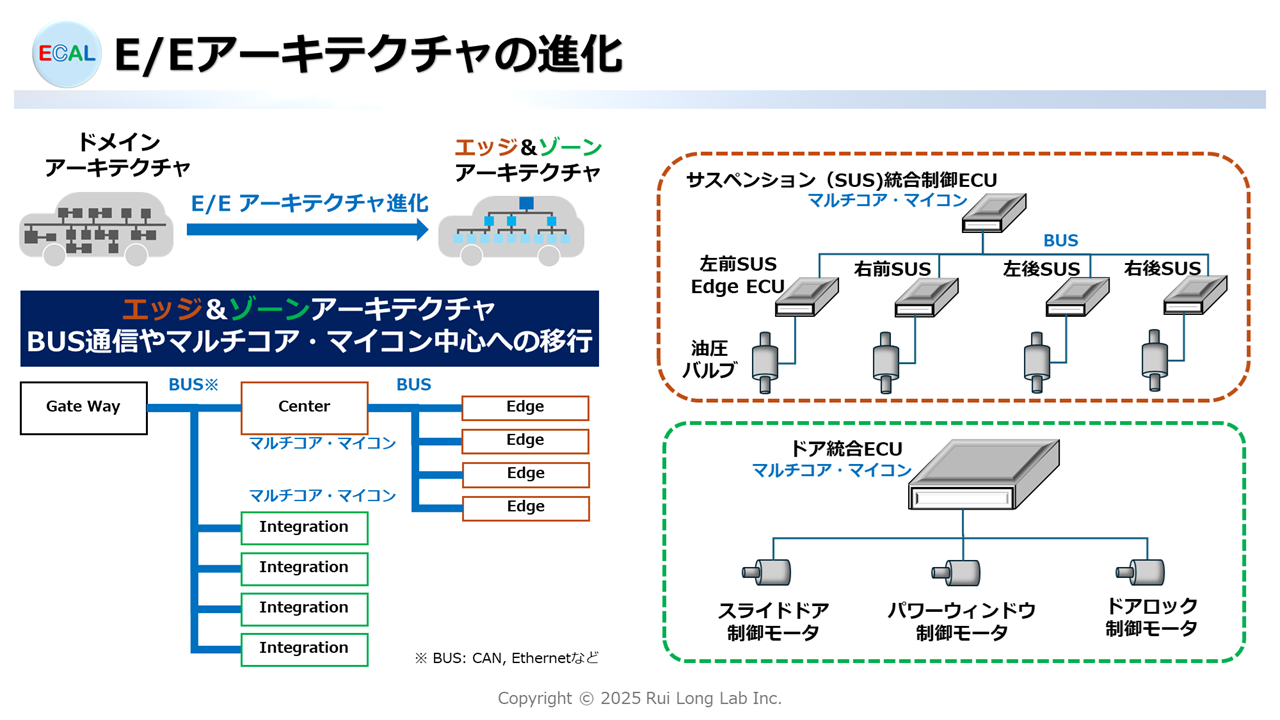

E/Eアーキテクチャの進化

E/Eアーキテクチャは、従来のドメインアーキテクチャは、エッジアーキテクチャやゾーンアーキテクチャへと移行しつつあります。これらの新しいアーキテクチャでは、BUS通信やマルチコアマイコンにおけるコア共通BUSが中心的な役割を担うようになります。

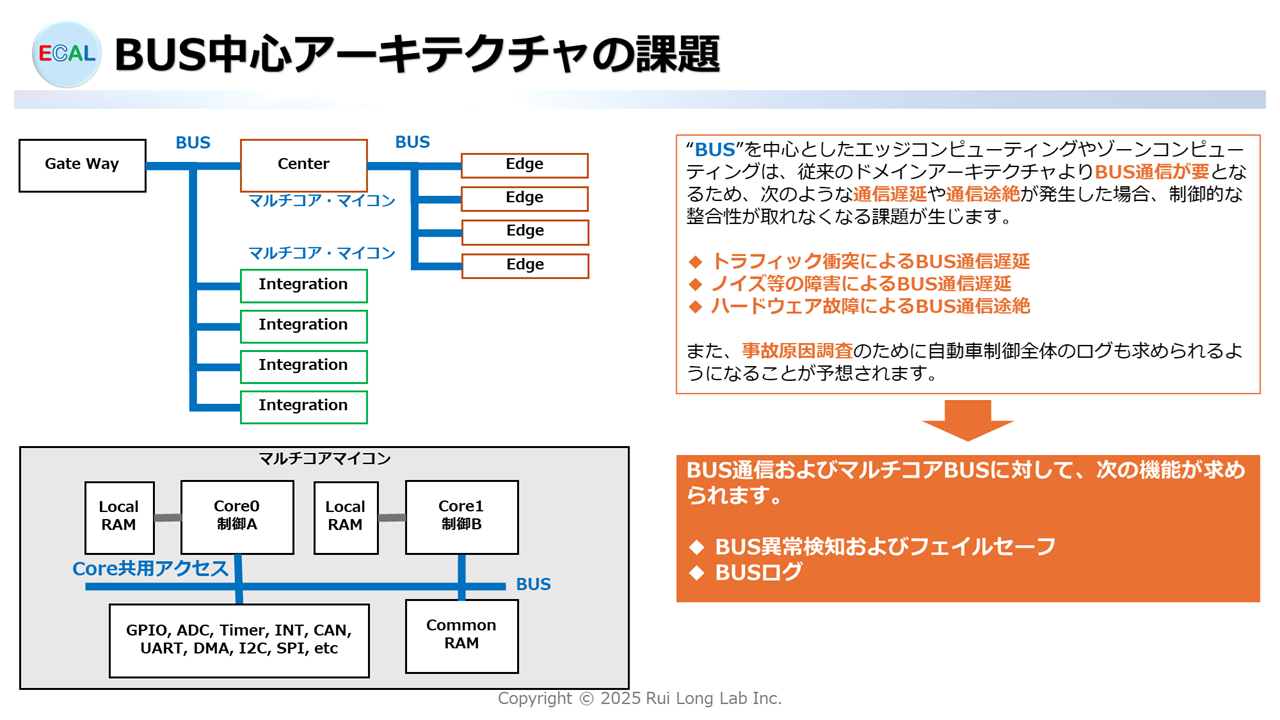

BUS中心アーキテクチャの課題

このようなアーキテクチャでは、下図のようにBUS通信やコア共通BUSがシステム全体の要となるため、通信遅延や通信途絶が発生すると、制御の整合性が保てなくなるという課題が生じます。また、事故原因調査のために自動車制御全体のログも求められるようになることが予想されます。

よって、BUS通信およびCore共有BUSに対して、次の機能が求められます。

- BUS異常検知およびフェイルセーフ

- BUSログ

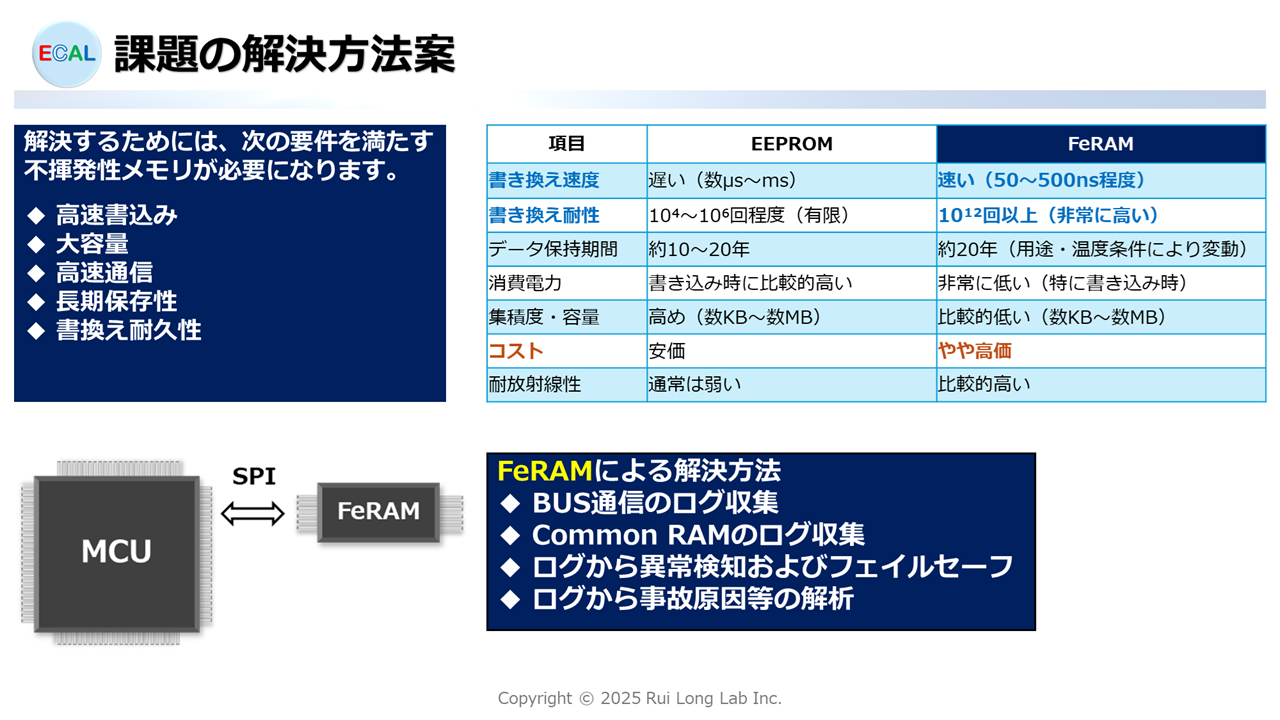

課題の解決方法案

その求められる機能を実現するためには、下図のような解決方法をご提案いたします。尚、本投稿はあくまで案であることをご理解ください。

RAMXEED社製FeRAM MB85RS4MTY仕様

| 項目 | 性能 | 備考 |

|---|---|---|

| メモリ容量 | 512 k × 8bit | |

| 通信速度 | 50Mbps | SPI |

| 書込み待ち時間 | ゼロ | |

| 書込み/読出し耐性 | 1014回 | |

| データ保持特性 | 50.4年(+85°C) 13.7年(+105°C) 4.2年(+125°C) | |

| 動作周囲温度 | -40°C ~ +125°C | |

| 動作電源電圧 | 1.8V~3.6V | |

| 品質/信頼性 | AEC-100準拠 | |

| 例: CAN IDログ数 ログ時間 | 78ID×8byte 6.06s | 計算条件: 500kbps, 111bit/ID, CAN BUS利用率30% |

| 例: Common RAMのログ数 ログ時間 | 600 byte 0.865s | 計算条件: 制御周期1ms |

ご興味のある方は、こちらからお問合せください。