この投稿では、マルチコア・マイコンの制御ソフトウェア構成の例を二つ紹介させていただきます。

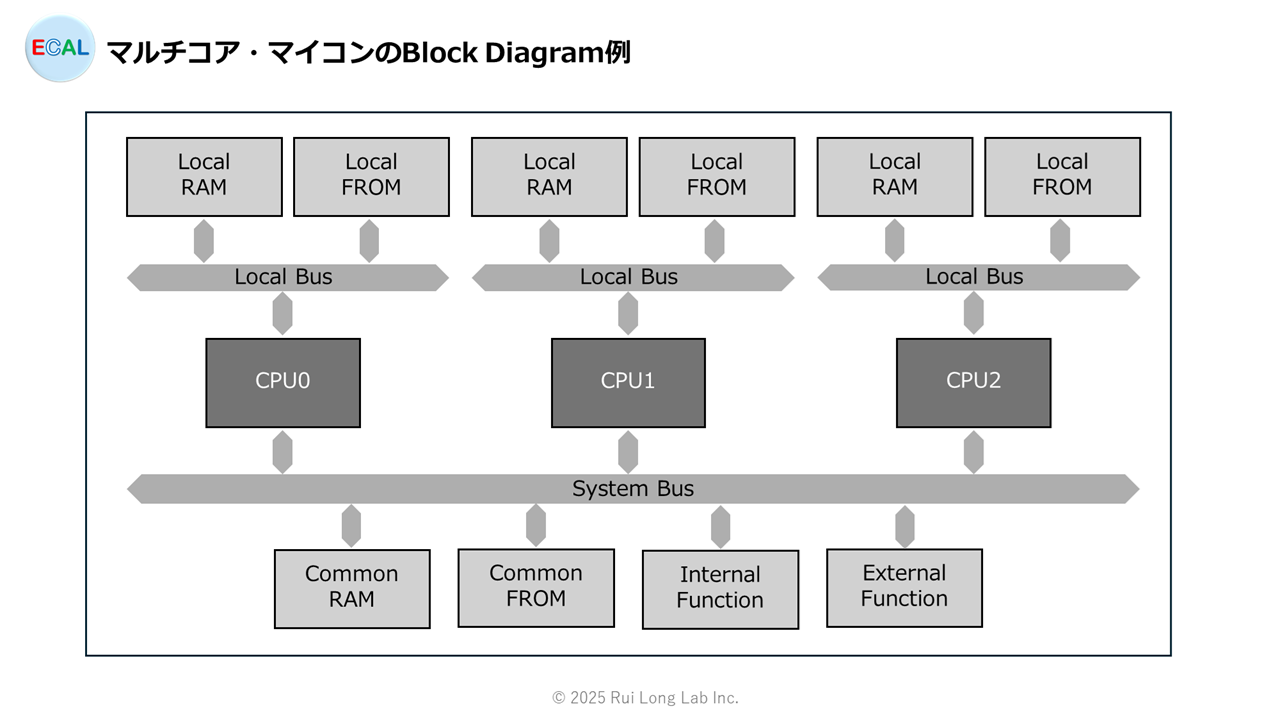

マルチコア・マイコンのBlock Diagramの例

マルチコア・マイコンのBlock Diagramは、下図のようなSMP(対称型マルチプロセッシング)のBlock Diagramを例として制御ソフトウェア構成を紹介したいと思います。

CPU別ソフトウェア機能配置の例

制御ソフトウェア構成およびCPU間インタフェースの例

制御ソフトウェア構成の例

制御ソフトウェア構成は、下図および下表のようにCPU毎に機能を分割します。尚、各CPUの処理時間に余裕があることを前提としています。

| CPU | ソフトウェア |

|---|---|

| CPU0 | 制御アプリケーションA 制御アプリケーションB 制御アプリケーションC |

| CPU1 | I/Oドライバ – 回路やIC、センサ、アクチュエータなどの操作および入出力ドライバ – HAL:GPIO, ADC, PWM, Pulse IO, SPI, I2C |

| CPU2 | 通信ドライバ – 通信アプリケーションおよび通信ミドルウェア – HAL:UART, CAN, LIN, Ethernet, EtherCAT |

CPU間インタフェースの例

CPU間インタフェースは、下図に示すとおり Common RAM を介して行います。

各CPUには専用の Write only Area を設け、処理周期ごとに1回だけデータを書き込みます。この書き込み処理は排他制御を行い、データの整合性を確保します。

他のCPUは、このWrite only Areaから必要な情報を読み取ります。

| Write | Read |

|---|---|

| CPU0: 制御アプリケーションA/B/C | CPU1: I/Oドライバ CPU2: 通信ドライバ |

| CPU1: I/Oドライバ | CPU0: 制御アプリケーションA/B/C |

| CPU2: 通信ドライバ | CPU0: 制御アプリケーションA/B/C |

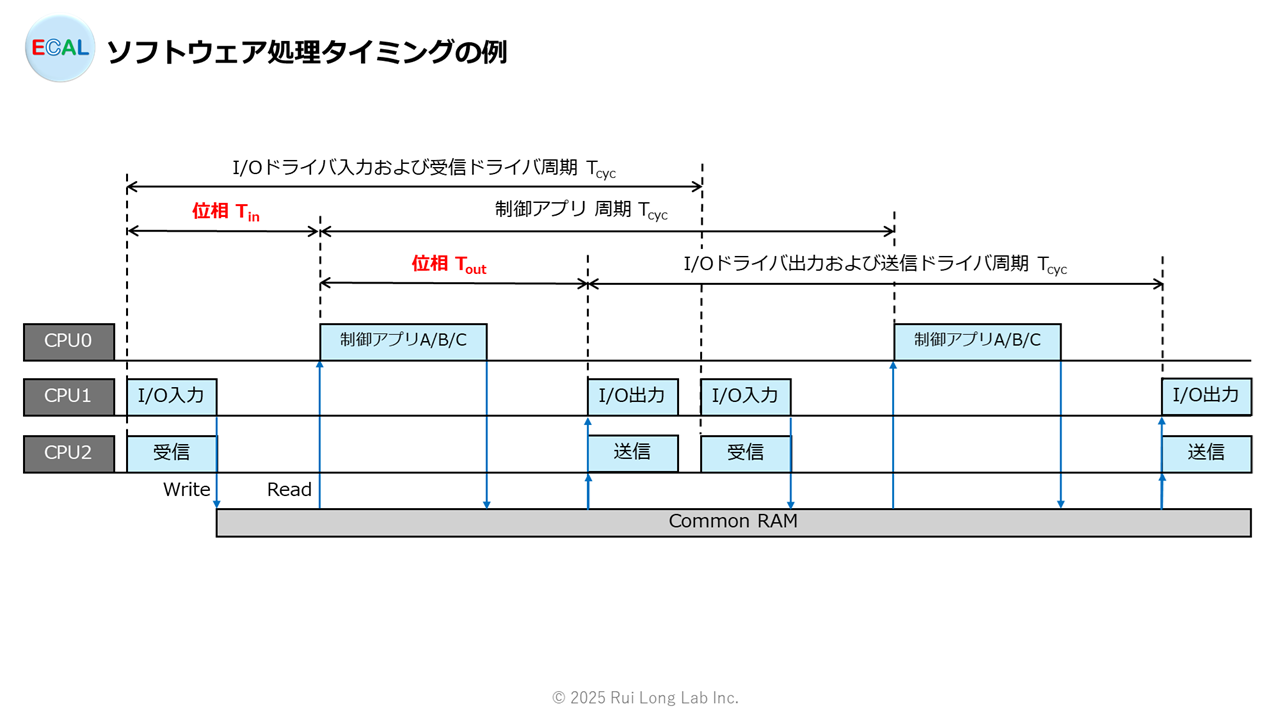

ソフトウェア処理タイミングの例

ソフトウェア処理タイミングは、下図に示すとおりです。

| ラベル | 時間 |

|---|---|

| Tcyc | CPU0: 制御アプリケーションA/B/Cの処理周期 CPU1: I/Oドライバの処理周期 CPU2: 通信ドライバの処理周期 |

| Tin | CPU1のI/Oドライバ入力およびCPU2の通信ドライバ受信の処理開始からCPU0の制御アプリケーション処理開始までの位相 注意: Tinは、I/O入力および受信の処理に要する最大時間に余裕時間を加えた値を示します。 これらの処理は、制御アプリケーションの実行開始前に完了している必要があります。 |

| Tout | CPU0の制御アプリケーション処理開始からCPU1のI/Oドライバ出力およびCPU2の通信ドライバ送信の処理開始までの位相 注意: Toutは、制御アプリケーションの最大処理時間に余裕時間を加えた値を示します。 I/O出力および送信の処理は、制御アプリケーションの完了後に実行する必要があります。 |

CPU別制御アプリケーション・I/Oドライバ配置の例

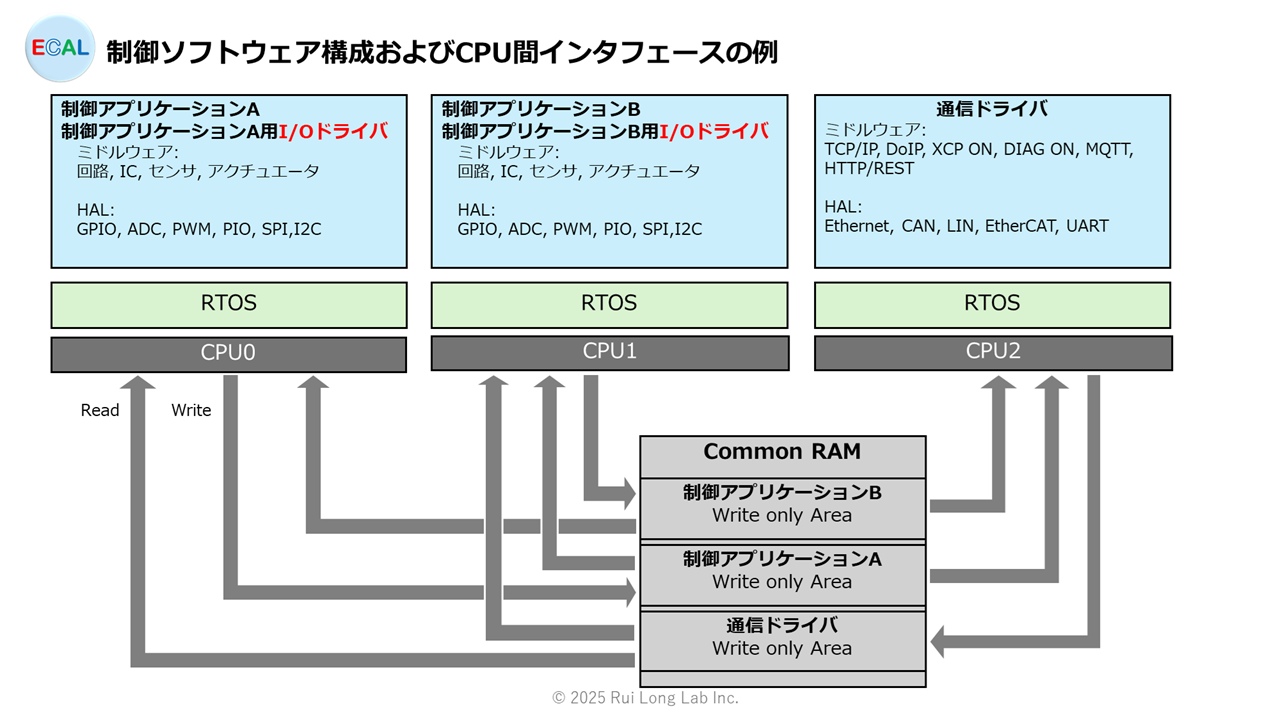

制御ソフトウェア構成およびCPU間インタフェースの例

制御ソフトウェア構成の例

制御ソフトウェア構成は、下図および下表のようにCPU毎に制御アプリケーションおよびI/Oドライバを分割します。尚、各CPUの処理時間に余裕があることを前提としています。

| CPU | ソフトウェア |

|---|---|

| CPU0 | 制御アプリケーションA 制御アプリケーションA用I/Oドライバ – 回路やIC、センサ、アクチュエータなどの操作および入出力ドライバ – HAL:GPIO, ADC, PWM, Pulse IO, SPI, I2C |

| CPU1 | 制御アプリケーションB 制御アプリケーションB用I/Oドライバ – 回路やIC、センサ、アクチュエータなどの操作および入出力ドライバ – HAL:GPIO, ADC, PWM, Pulse IO, SPI, I2C |

| CPU2 | 通信ドライバ – 通信アプリケーションおよび通信ミドルウェア – HAL:UART, CAN, LIN, Ethernet, EtherCAT |

注意: MCUの機能は共有資源であるため、制御アプリケーションA用I/Oドライバと制御アプリケーションB用I/Oドライバは共用しないでください。

例:

・制御アプリケーションA用I/Oドライバ:ADC Gr0 ch0, ch1, ch2

・制御アプリケーションB用I/Oドライバ:ADC Gr0 ch3, ch4

上記のようにADC Gr0を両方で使用すると、競合により不具合が発生する可能性があります。

この場合は、いずれかのI/OドライバをADC Gr1など別のリソースに割り当ててください。

CPU間インタフェースの例

CPU間インタフェースは、下図に示すとおり Common RAM を介して行います。

各CPUには専用の Write only Area を設け、処理周期ごとに1回だけデータを書き込みます。この書き込み処理は排他制御を行い、データの整合性を確保します。

他のCPUは、このWrite only Areaから必要な情報を読み取ります。

| Write | Read |

|---|---|

| CPU0: 制御アプリケーションA | CPU1: 制御アプリケーションB CPU2: 通信ドライバ |

| CPU1: 制御アプリケーションB | CPU0: 制御アプリケーションA CPU2: 通信ドライバ |

| CPU2: 通信ドライバ | CPU0: 制御アプリケーションA CPU1: 制御アプリケーションB |

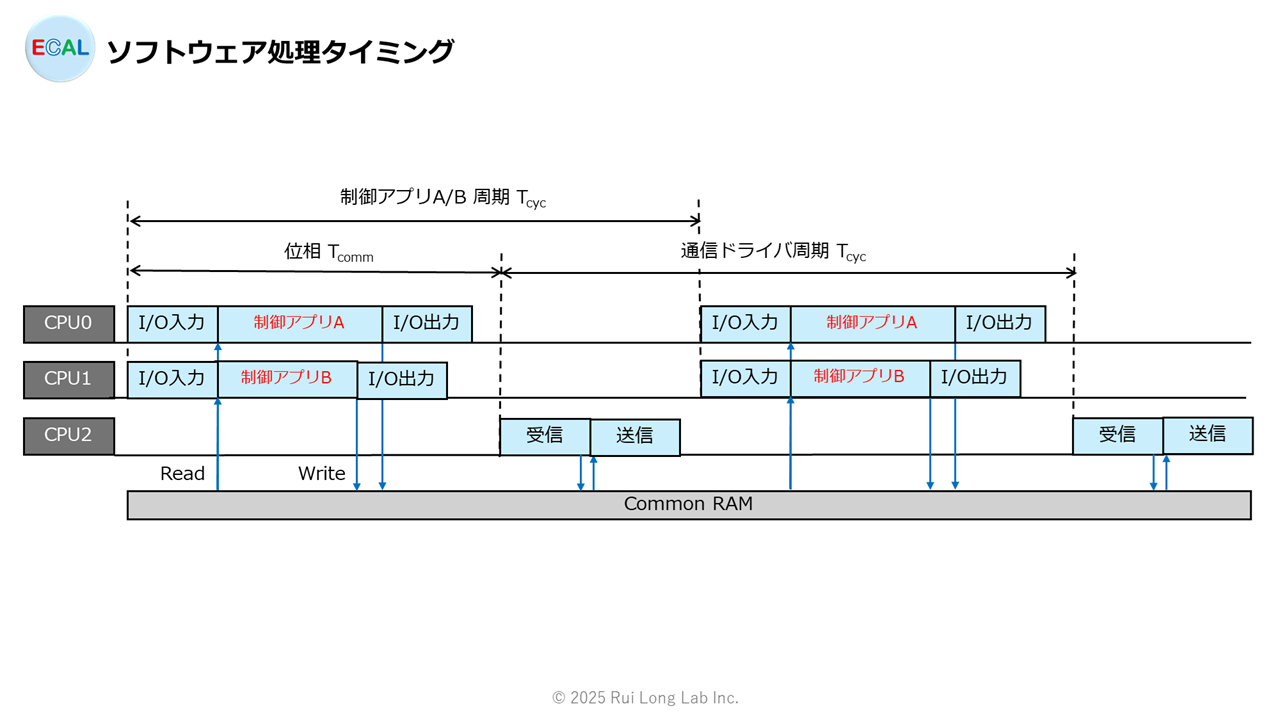

ソフトウェア処理タイミングの例

ソフトウェア処理タイミングは、下図に示すとおりです。

注意:

この例では、制御アプリケーションAと制御アプリケーションBの連動性が低い場合の処理タイミングです。連動性が高い場合は、処理タイミングに位相を設けてください。

| ラベル | 時間 |

|---|---|

| Tcyc | CPU0: 制御アプリケーションAの処理周期 CPU1: 制御アプリケーションBの処理周期 CPU2: 通信ドライバの処理周期 |

| Tcomm | CPU0およびCPU1の制御アプリケーションA/BおよびI/Oドライバ入力の処理開始からCPU2の通信ドライバの処理開始までの位相 |