本文将介绍两种多核微控制器的控制软件架构示例。

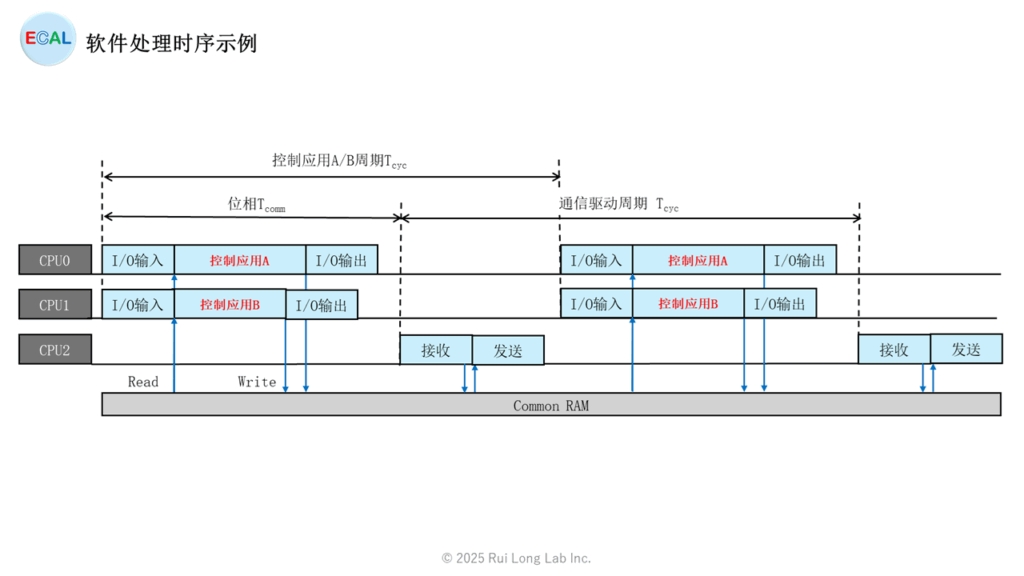

多核微控制器框图示例

多核微控制器的功能框图,将以如下图所示的SMP(对称多处理)功能框图为例,介绍控制软件的构成。

CPU软件功能配置示例

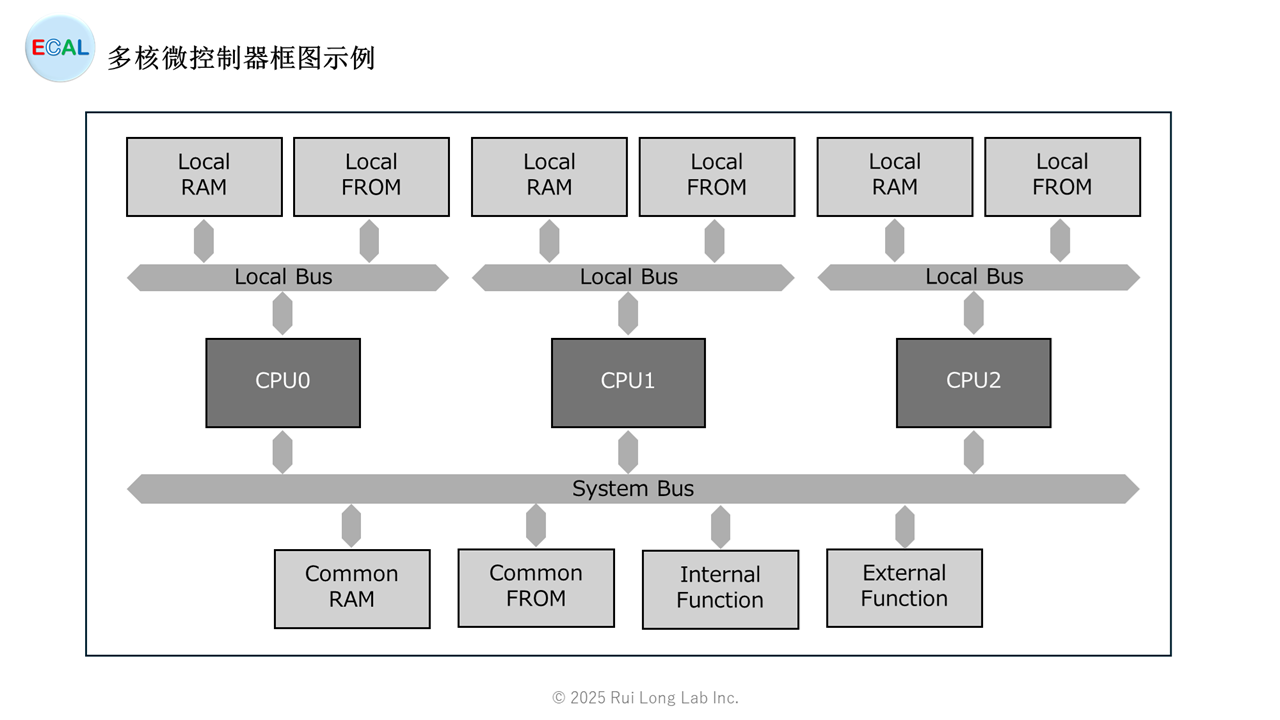

控制软件配置和 CPU 到 CPU 接口示例

控制软件配置示例

如下图和下表所示,控制软件配置分为每个 CPU 的功能。假定每个 CPU 都有足够的处理时间。

| CPU | 软件 |

|---|---|

| CPU0 | 控制应用A 控制应用B 控制应用C |

| CPU1 | I/O驱动程序 – 电路和集成电路、传感器、致动器驱动器 – HAL:GPIO, ADC, PWM, Pulse IO, SPI, I2C |

| CPU2 | 通信驱动程序 – 通信应用程序和通信中间件 – HAL:UART, CAN, LIN, Ethernet, EtherCAT |

CPU 到 CPU 接口示例

CPU间接口通过Common RAM实现,如下图所示。

每个CPU都设有专用的只写区域,每处理周期仅写入一次数据。该写入操作实施排他控制,以确保数据一致性。

其他CPU从该只写区域读取所需信息。

| Write | Read |

|---|---|

| CPU0: 控制应用A/B/C | CPU1: I/O驱动程序 CPU2: 通信驱动程序 |

| CPU1: I/O驱动程序 | CPU0: 控制应用A/B/C |

| CPU2: 通信驱动程序 | CPU0: 控制应用A/B/C |

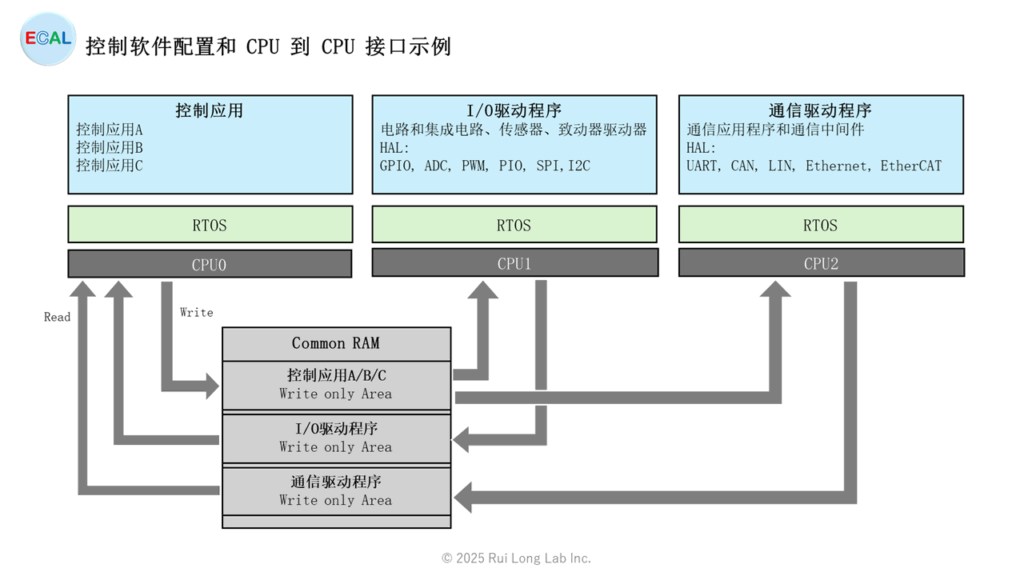

软件处理时序示例

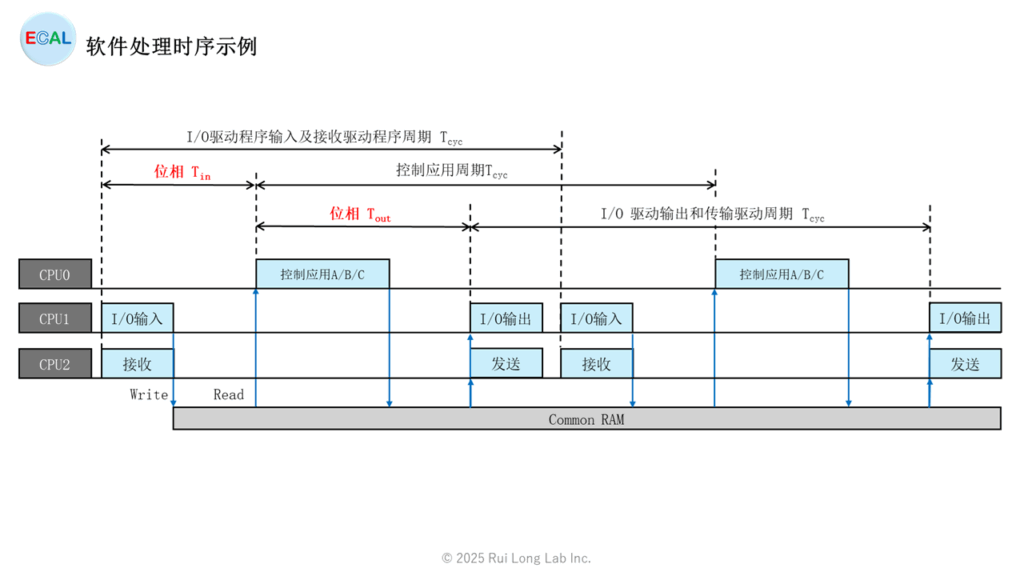

软件处理时序如下图所示。

| 标签 | 时间 |

|---|---|

| Tcyc | CPU0: 控制应用程序 A/B/C 的处理周期 CPU1: I/O 驱动程序处理周期 CPU2: 通信驱动程序的处理周期 |

| Tin | 从CPU1的I/O驱动程序输入及CPU2的通信驱动程序接收处理开始到CPU0的控制应用程序处理开始之间的相位。 注意: Tin表示I/O输入及接收处理所需的最大时间加上裕量时间的值。 这些处理必须在控制应用程序开始运行之前完成。 |

| Tout | 从CPU0控制应用程序处理开始到CPU1 I/O驱动程序输出及CPU2通信驱动程序发送处理开始的相位。 注意: Tout表示控制应用程序的最大处理时间加上裕量后的值。 I/O输出及发送处理必须在控制应用程序完成后执行。 |

CPU分控应用程序与I/O驱动程序配置示例

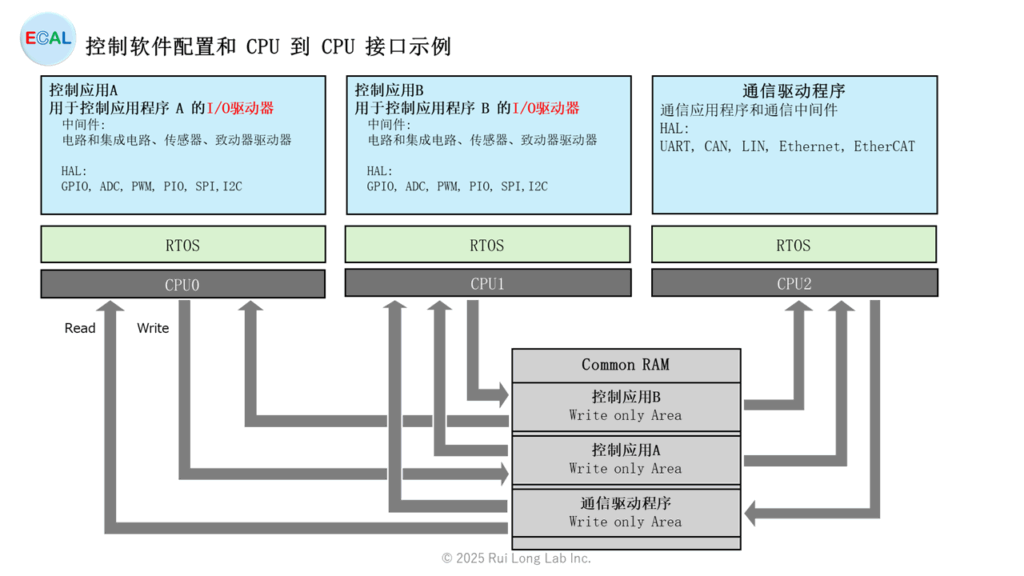

控制软件配置和 CPU 到 CPU 接口示例

控制软件配置示例

控制软件架构如下图及下表所示,将控制应用程序和I/O驱动程序按CPU进行分割。此外,该设计基于各CPU处理时间充裕的前提。

| CPU | 软件 |

|---|---|

| CPU0 | 控制应用A 用于控制应用程序 A 的I/O驱动器 – 电路和集成电路、传感器、致动器驱动器 – HAL:GPIO, ADC, PWM, Pulse IO, SPI, I2C |

| CPU1 | 控制应用B 用于控制应用程序 B 的I/O驱动器 – 电路和集成电路、传感器、致动器驱动器 – HAL:GPIO, ADC, PWM, Pulse IO, SPI, I2C |

| CPU2 | 通信驱动程序 – 通信应用程序和通信中间件 – HAL:UART, CAN, LIN, Ethernet, EtherCAT |

注意:由于MCU功能属于共享资源,请勿将控制应用程序A的I/O驱动程序与控制应用程序B的I/O驱动程序混用。

例:

・控制应用程序A的I/O驱动程序:ADC Gr0 ch0, ch1, ch2

・控制应用程序B的I/O驱动程序:ADC Gr0 ch3, ch4

如上所述,若ADC Gr0被两个应用程序同时使用,可能因资源冲突导致故障。

此时请将其中一个I/O驱动程序分配至ADC Gr1等其他资源。

CPU 到 CPU 接口示例

CPU间接口通过下图所示的Common RAM实现。

每个CPU均设有专用的只写区域,每处理周期仅写入一次数据。该写入操作采用排他控制机制,确保数据一致性。

其他CPU从该只写区域读取所需信息。

| Write | Read |

|---|---|

| CPU0: 控制应用A | CPU1: 控制应用B CPU2: 通信驱动程序 |

| CPU1:控制应用B | CPU0: 控制应用A CPU2: 通信驱动程序 |

| CPU2: 通信驱动程序 | CPU0: 控制应用A CPU1: 控制应用B |

软件处理时序示例

软件处理时序如下图所示。

注意:本例说明控制应用程序A与控制应用程序B联动性较低时的处理时机。若联动性较高,请在处理时机中设置相位。

| 标签 | 时间 |

|---|---|

| Tcyc | CPU0: 控制应用程序 A 的处理周期 CPU1: 控制应用程序 B 的处理周期 CPU2: 通信驱动程序的处理周期 |

| Tin | 从CPU0和CPU1的控制应用程序A/B及I/O驱动程序输入处理开始到CPU2的通信驱动程序处理开始的间的相位。 |