在本文中,我想针对 E/E (电子/电子)架构中的一个新挑战提出一个解决方案。

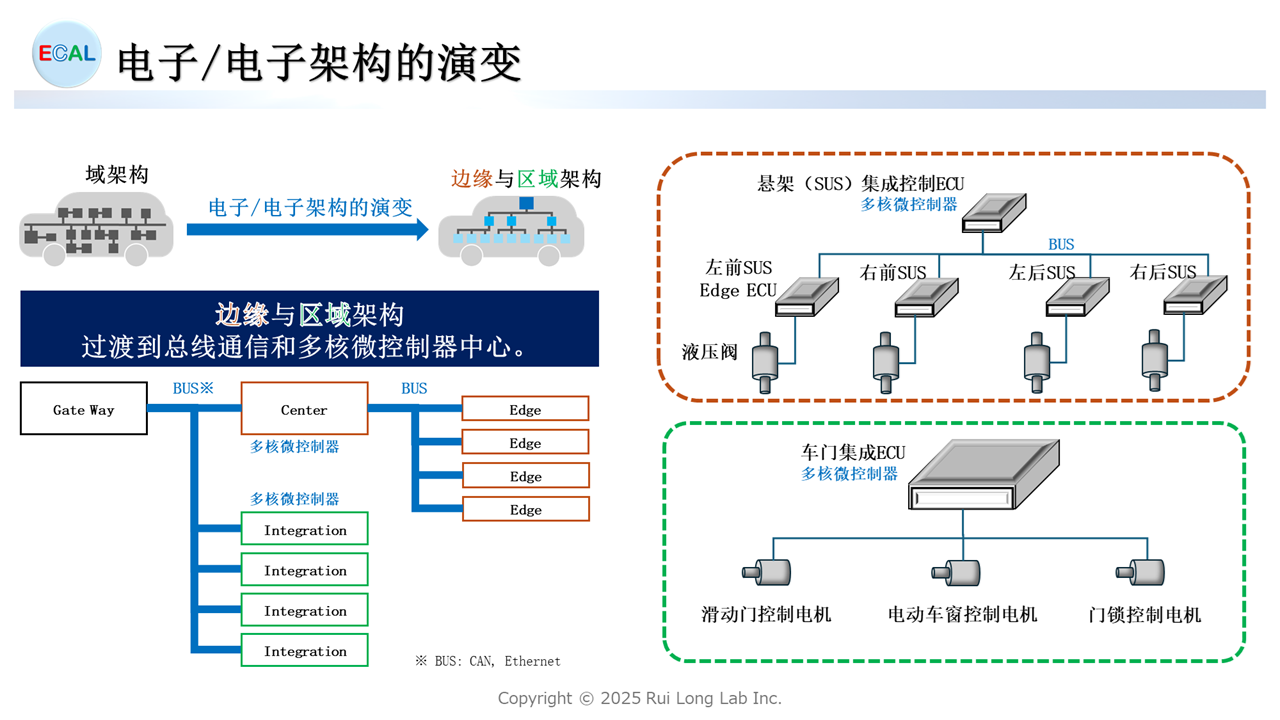

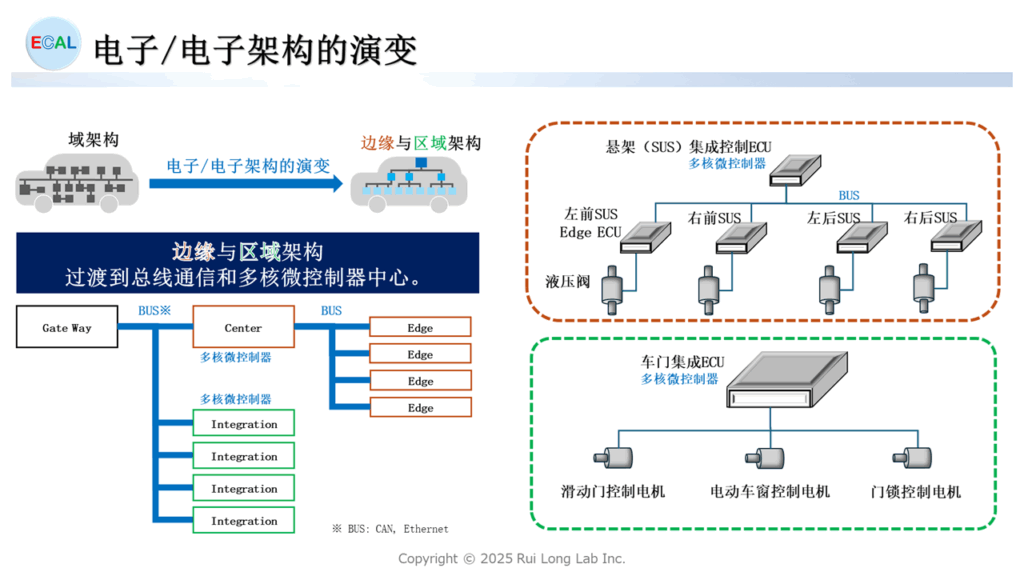

E/E架构的演变

E/E架构正逐步从传统的域架构向边缘架构和区域架构转型。在这些新型架构中,总线通信以及多核微控制器中的核心共享总线将承担核心作用。

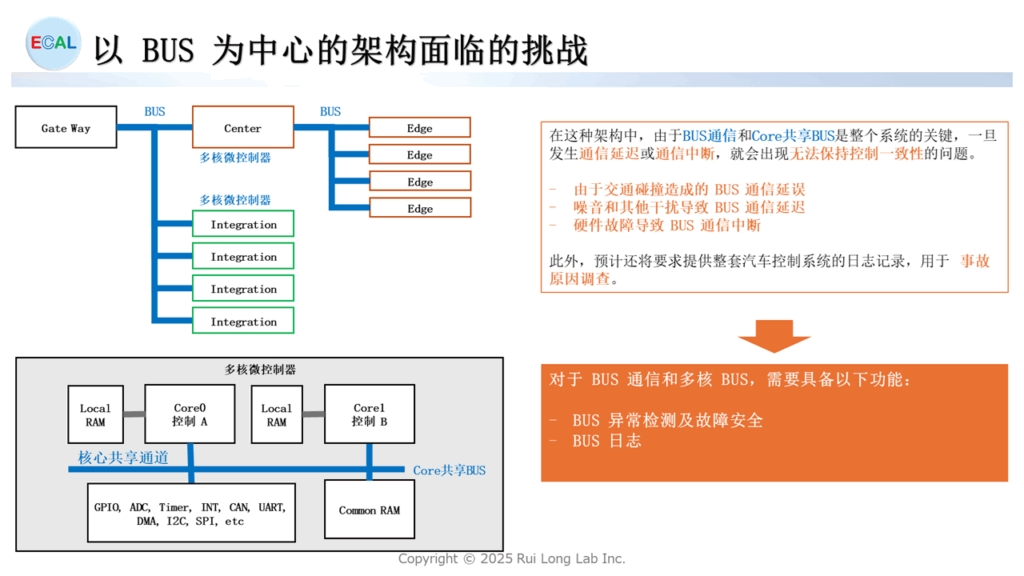

以 BUS 为中心的架构面临的挑战

在这种架构中,如下图所示,总线通信和核心共用总线成为整个系统的关键枢纽。因此,一旦发生通信延迟或通信中断,就会导致控制一致性无法维持的问题。此外,预计未来为调查事故原因,将需要获取整车控制系统的完整日志记录。

因此,总线通信和核心共享总线需要以下功能。

- BUS 异常检测及故障安全

- BUS日志记录

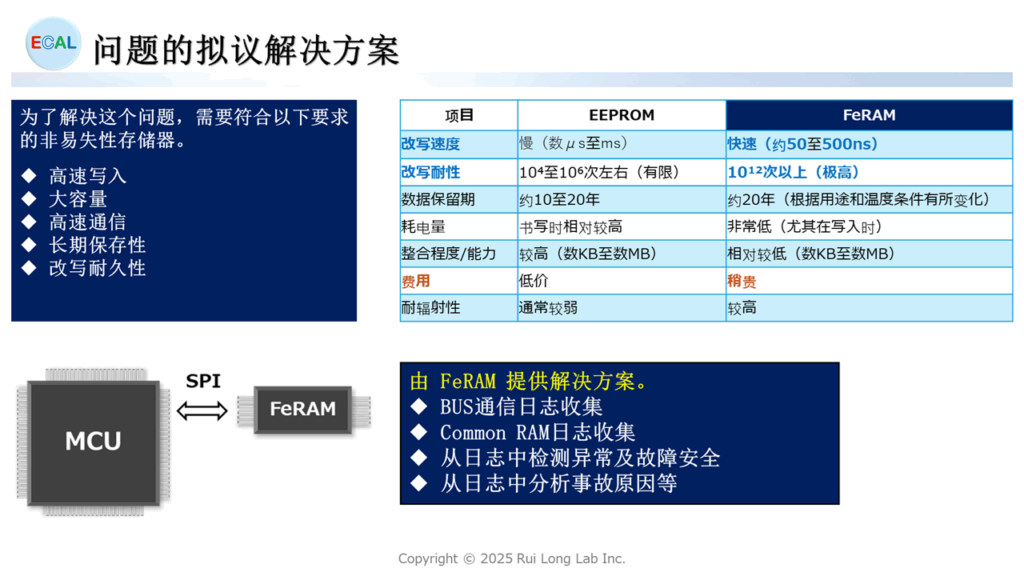

问题的拟议解决方案

为了实现所需的功能,现提出以下解决方案。请注意,本意见仅为建议。

RAMXEED FeRAM MB85RS4MTY 规格

| 项 | 性能 | 备注 |

|---|---|---|

| 内存容量 | 512 k × 8bit | |

| 通讯速度 | 50Mbps | SPI |

| 写时间 | 零 | |

| 写入/读取容差 | 1014回 | |

| 数据保留特性 | 50.4年(+85°C) 13.7年(+105°C) 4.2年(+125°C) | |

| 工作环境温度 | -40°C ~ +125°C | |

| 工作电源电压 | 1.8V~3.6V | |

| 质量/可靠性 | 符合 AEC-100 标准 | |

| 例如:CAN ID 日志数 日志时间 | 78ID×8byte 6.06s | 计算条件: 500kbps, 111bit/ID, CAN BUS利用率30% |

| 例如:普通RAM的日志数量 日志时间 | 600 byte 0.865s | 计算条件: 控制周期 1ms |

如果您对此感兴趣,请点击此处与我们联系。